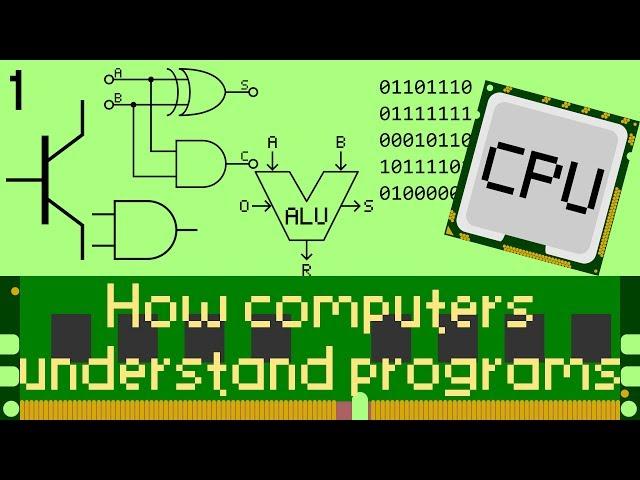

How computers understand programs: From transistors to a CPU (1/3)

Комментарии:

Ich bin Bruno

Ответить

At first I thought I got an A in DLD (Digital Logic Design) so this video is not for me

But you can always learn something new ... Thanks for giving me a new way to look at things❤️

fantastic video, sad there is only one video

Ответить

Nice

Ответить

Amazin! Congrats!

Ответить

i just love your sense of humor. amazing video.

Ответить

عليك ان تختار تنسيق الالوان جيدا , فعندما تضع الاخضر مع الابيض هذا يسبب لنا تشويها في النظر , و كأنك تلبس نظارة شخص نظره ضعيف.

Ответить

you sum up my whole first year of engineering in this video

Ответить

I've been looking for this detail, the physics plus abstraction for years! Not that I fully understand this, but I will watch multiple times. I also love the humor and graphics. Thank you thank you!

Ответить

The market is profitable if you are using a really good broker or account manager to help out with trades or provide good signals

Ответить

Thanks 😊❤

Ответить

Beautifully done

Ответить

It wud bi match bätter if ju wud häv äxpläin iet in yoa näitif lenguätsch. Spaß beiseite: Ich finde es echt schwierig dir zu folgen. Auf deutsch hätte ich es besser gefunden. Klar, nicht so die Reichweite. Aber es gibt genügend Erklärungen auf Englisch. Ein Popschutz vor dem Mikrofon wirkt übrigens auch wunder ^^. Oder zumindest einen lowcut eq filter.

Ответить

Great visualization of how the computers actually works😮😮

Ответить

It would be much better if you followed your own natural accent not accent of native english speaking guys.

Ответить

Sir please make more and more videos

Ответить

Thank you sir

Ответить

❤

Ответить

Gutes Video 👍 schade dass es so aussieht als würde die Serie nicht fortgesetzt werden

Ответить

this is too good, great job, too bad you didn't follow the series, but great explanation

Ответить

More pls

Ответить

I am more confused now more than ever lol 😂

Ответить

Great explanation. Congrats!

Ответить

Excellent, vraiment. Le mieux que j'ai vu, by far. Merci, continu ❤

Ответить

Good Job

Ответить

Perfect Explanation.

Ответить

It requires good knowledge of physics, mathematics and electronics to understand the hardware and system operating software, and how assembly programming language can have an insight of the hardware and influence on the hardware performances, and that's why you guys must have at least good knowledge of computer science at university levels to do so

Ответить

A half Adder has no memory, consisting of an XOR gate and AND gate

with the machine language or binary system in which when there is a flow of negative charge carried by oscillating free electrons, and simultaneously a flow-like transmission of positive charge from cation to cation or from positively charge ion to positively charged ion, the voltage signal is interpreted as on = 1, when there is not any flow of charge , the signal is interpreted as off = 0

Here is the truth table for an half-Adder

Input Carry Output

A B 0ut Sum

0 0 0 0

0 1 0 1

1 0 0 1

1 1 1 0

We can see that the XOR gate is different from the OR gate only in the last inputs, where the sum of the XOR gate = 0 and 1 is carried out into an AND gate

A---------------- half ---------- sum (output)

B---------------- Adder ---------- carry out

That's a Hal-f Adder. it looks like a rectangle with 2 inputs A & B, one out put and one carry out

Unlike an Half-Adder, a Full Adder has a memory, consisting 2 XOR gates in continuous connection, 2 AND gates in parallel connection to the XOR gates , and one OR gate. The sum comes out through the 2 XOR gate. The carry out comes out through the OR gate. There is also a clock to control the carry in signal ----> 3 different inputs clock, A & B , the outputs are the same as the Half-Adder. Since a Full-Adder has a memory, it is called as " a latch"

Basically, the carried out voltage signal of one Half-Adder is fed into one of the inputs of the next Half-Adder of which the other input is a clock to control the carried in voltage signal

Here is the truth table for the Full-Adder

A B C Carry Sum

0 0 0 0 0

0 0 1 0 1

0 1 0 0 1

0 1 1 1 0

1 0 0 0 1

1 0 1 1 0

1 1 1 1 1

-----------------------------------------------------------------------------------------------------------------------------------------------------

8 Half-Adder connected together in that way make a 4 Full-Adder, or an 8 outputs or 8 bit Hal-Adder, which is called as "an 8 bit Ripple Carry Adder. The max scalar or quantity value of storable bit for an 8 bit Ripple Carry Adder in terms of base 10 is 256 . If there is a carry into 9th bit, the sum will become too large to fit into the 8 bit Adder, which will cause errors or unexpected behaviour in the ALU, and is caused as an "Overflow" . We can fix the problem of overflow by adding more Full-Adders to the 8 bit Adders, such as 16 bit Half- Adder , 32 bit Half-Adder, 64 bit Half-Adder to the circuit.

When we feed an output back into one of the inputs, the circuit of gates is called as "a latch" because it latches a particular value. Putting such bits which are the machine language in binary system is called as writing data into memory, and getting such stored bits in the circuits of gates is defined as reading data

With a clock to control the gate of the latch, or to open or close the gate of inputs of the circuit is defined as a gated latch, and that's why we have "write enable" , and " read enable" functions. We can put. 8 gated latches together side by side to save 8 bits of info , and the group of the gated latches make an 8 bit "register" . Similarly we can increase the number of gated latches to make 32 bit, 64 bit registers

To write data to the registers, we will have to enable all of the gated latches, by sending a voltage signal which corresponds to 1 in binary system, along a single wire which connects to all the latches' "enable inputs"

The side-by side design for gated latches is workable only for a small number of gated latches, but not for a larger number of gated latches. For instance, in a 64 bit register containing 64 gated latches, we will need 64 wires running to the inputs, 64 other wires running to the outputs, and one wire to enable all the gated latches----> the number of wire = 64 + 64 + 1 = 128

For a 256 bit register, we will need (256 + 256 + 1) wires = 513v wires, The size of the CPU is too small for that hardware design or architecture. Hen, we must make the circuit compacted by applying the idea of a 256 by 256 matrix, in which we arrange the gated in a grid, but no longer in a row . We use an AND gate to control the gates of 256 gated latches. Example, if we want to open a gated latch at a certain location in the grid, the AND gate will output a 1 only when both the column wire and the row wire of the gated larch are transmitting a voltage signal , which is decoded as 1 in binary system. Hence, in order to for a latch to become " write- enabled" , the row wire, the column wire and the "enable wire" must be sending a voltage signal or 1 in binary system. Only that gated latch is activated at the given time, while all other gated latches are disabled or not active.

That's a brief explain for you to understand some basic design of computer hardware , and how info is stored and transmitted in a computer's CPU & ALU

Best explanation

Ответить

Good job

Ответить

Very nice. Please do the next videos.

Ответить

Gdzie jest 2/3 i 3/3?

Ответить

They do not

Ответить

What a narration!

Ответить

The answer is "they don't understand", they are machines

Ответить

This video is made of gold

Ответить

Where's part 2

Ответить

Please continue your series

Ответить

There are no 1s or 0s, just high/low states.

This linguistic fault has misled this a generation.

Still waiting for part 2

Ответить

the first genius i found on youtyube since 2005

Ответить

So good 🎉 Wish you'd continue the series

Ответить

They don't

Ответить

Very clear explained. Thank you.

Ответить

Brain combines ALU, ram, cache; control unit is more like old cortex with all vegetative functions.

Ответить

Yuck audio

Ответить

You sure your OR table is right, I am afraid it is not.

Ответить