Комментарии:

Interesting topic sire

Ответить

MERKO LUND KUCH SMJH NHI AAYA

Ответить

Why are you talking like that !

Ответить

This was just perfect by you sir!

Ответить

Why do you always take a negative edge clock, any specific reason?

Ответить

So comfortable , so professional.

Ответить

You are amazing , thank you !

Ответить

If q3 is 1 then howcome you have take d2 as 0

Ответить

Usually the most adjacent flipflop is the lsb but in registers the output from that flipflop is taken as msb why?

Ответить

Sir can you please tell me why the clock is set down in the table?

Ответить

Sir what is the meaning of downward arrow ??? In truth table...

Ответить

thank you very much

Ответить

You don't know how to teach man. Please have some respect for others time.

Ответить

before sem NETFLIX while sem NESO 🥶🥶

Ответить

My teacher completely skipped the sequential logic circuits just because its hard!

Your videos have helped me so much!

I really appreciate it!

Can I switch from Jk to D? Can I connect a synchronous counter to JK and convert it to D?

Ответить

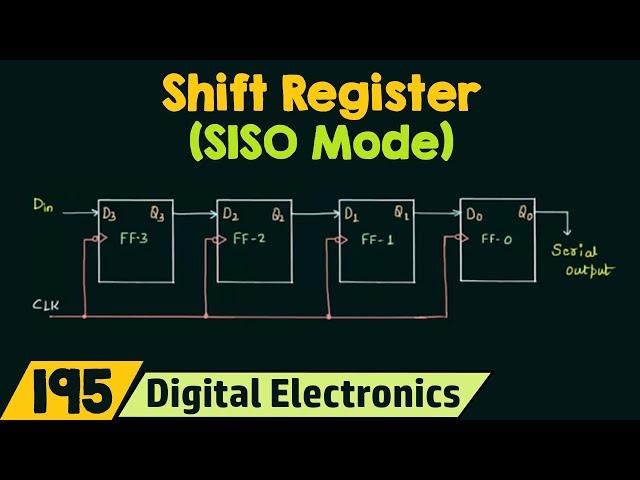

Why Does SISO Shift Register Has Falling Clock Edge ?

Ответить

Honestly speaking just because of only you I passed my exam

Ответить

Explanation was great.. But You should have made separate TABLE FOR D3,D2,D1,D0..

(For better understanding)

"What I have to do?" vs. "What do I have to do?", the latter is correct.

Ответить

Thanks for your presentation. It would be better to understand if you use input with the same bit. For example, 1010

Ответить

Super

Ответить

This reminds me on a project of years ago. It was used to create a audio echo with using serial shift registers. They called it a bucket line storage and used 8 bit wide and 1k long registers. The delay with running through those registers produced an echo effect.

Ответить

❤️

Ответить

confusion :- why there is Q3, Q2, Q1, Q0 in output

here we are using SISO , So there should be only output at Q0 ???

if i am wrong then why ???

This channel is life saver for enginering students...

Ответить

Thank you sir

Ответить

thanks so much !

Ответить

awesome

😀

Thank you for helping the students from your unique and wonderful teaching and clearing the concepts ☺

Ответить

These videos are simply excellent for students, hobbyists and all those who keep learning for a lifetime !

Ответить

nice...

Ответить

I joined in a core company. Company told me to watch Neso academy videos for learning

Ответить

How does this satisfy the flip-flops' hold time?

Ответить

Thank you a lot!!

Ответить

thank you

Ответить

Anyone from ESTIN? 🤟😂

Ответить

Hi. Can you pls make some videos on Serial Receivers for digital logic? I dont know how to design them or the concept. Ty!

Ответить

Yes , very good

Ответить

So this kind of register doesn't storage any data, it only receives data and sends that data.

Ответить

Hoy la academia de Neso me dio una gran introducción para mi conferencia. Gracias👌

Ответить

does the siso register store this data for long and whenever we want the output we request it, or the output comes out as soon as the signal is applied? if it's the second case then what would it benefit us if the output signal is equal to the input but just delayed by few micro-seconds?

Ответить

Do anybody knows in what board or app or something that he is writing

Ответить

Don't we need any load(which you told in the previous lecture) to store that "1111"

Ответить

how come when q3 is 1, d2 is 0 if they are connected? this is the first pulse

Ответить